这里讨论的 Cache 和主存均采用 SRAM【因为使用 DRAM 还需考虑地址线行列复用的情况】。设当前 MAR 的位数是 24 位,MDR 的位数是 32 位,按字编址,Cache的行数是 64,主存内的每个块的大小是 128 个字。

由现在的条件可以推出:

- 主存内可寻址数是 2^{24} 个;

- 主存内每个存储单元的容量是 4B;

- 主存总量是 2^{24} × 4\text{B};

- 主存被分为 2^{17} 个存储块;

- Cache的行号占地址结构中的 6 位。

直接映射

| 标记 | Cache行号 | 块内地址 |

|---|

直接使用 \text{Cache}_{\;\text{row-num}} = \small{主存块号}\;\text{mod}\;\text{Cache}_{\;\text{total-num}} 计算当前主存块应该被映射到哪个 Cache 行中。

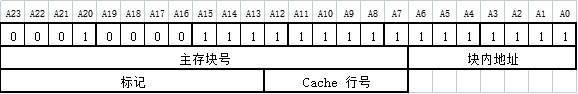

例如,当前的主存地址是 0x10FFFF,应当先展开为 24 位的二进制格式,即:

0001 0000 1111 1111 1111 1111

显然,根据之前所推出的数据,可以知道

CPU在访存时,会先读中间的 Cache 行号,然后把该行对应的标记提出来和欲访存的主存块号前11位作比较,如果相等并且有效位置是 1,那就说 Cache 命中,直接读取该行块内地址中的数据,引向 MDR。如果不相等或者有效位置是 0,那么不命中,要从主存中获取,然后替换当前 Cache 行中的主存块,并且有效位置设 1,接着把地址中的对应数据送给 CPU。